Page 3 - Tchistyakov2_12_16_terra.indd

P. 3

ОБЗОРЫ БЕСПРОВОДНЫЕ ТЕХНОЛОГИИ

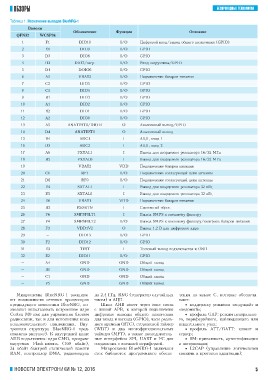

Таблица 1. Назначение выводов BlueNRG-1

Выводы Обозначение Функция Описание

QFN32 WCSP34 I/O Цифровой ввод/вывод общего назначения (GPIO)

I/O GPIO

1 F1 DIO10 I/O GPIO

I/O Вход загрузчика/GPIO

2 E1 DOI9 I/O GPIO

I/O Подключение батареи питания

3 D3 DIO8 I/O GPIO

I/O GPIO

4 D2 DIO7/загр. I/O GPIO

I/O GPIO

5 D1 DOIO6 I/O GPIO

I/O GPIO

6 A3 VBAT3 Аналоговый выход/GPIO

O Аналоговый выход

7 C2 DIO5 O АЦП, вход 1

I АЦП, вход 2

8 C3 DIO4 I Вывод для кварцевого резонатора 16/32 МГц

I Вывод для кварцевого резонатора 16/32 МГц

9 B1 DIO3 I Подключение батареи питания

VDD Подключение согласующей цепи антенны

10 A1 DIO2 I/O Подключение согласующей цепи антенны

I/O Вывод для кварцевого резонатора 32 кГц

11 B2 DIO1 I Вывод для кварцевого резонатора 32 кГц

I Подключение батареи питания

12 A2 DIO0 VDD Системный сброс

I Выход SMPS к внешнему фильтру

13 A5 ANATEST0/DIO14 I Выход SMPS к внешнему фильтру/контроль батареи питания

I/O Вывод 1,2 В для цифрового ядра

14 D4 ANATEST1 O GPIO

I/O GPIO

15 B4 ADC1 I/O Тестовый вывод подключается к GND

I GPIO

16 D5 ADC2 I/O Общий вывод

GND Общий вывод

17 A6 FXTAL1 GND Общий вывод

GND Общий вывод

18 B5 FXTAL0 GND

19 – VBAT2

20 C6 RF1

21 D6 RF0

22 E4 SXTAL1

23 E5 SXTAL0

24 E6 VBAT1

25 B3 RESETN

26 F6 SMPSFILT1

27 F4 SMPSFILT2

28 F3 VDD1V2

29 – DIO13

30 F2 DIO12

31 E3 TEST

32 E2 DIO11

– A4 GND

– B6 GND

– C1 GND

– F5 GND

Микросхемы BlueNRG-1 расширя- на 2,4 ГГц, RNG (генератор случайных чения на языке С, которые обеспечи-

ют возможности сетевых процессоров чисел) и АЦП. вают:

предыдущего поколения BlueNRG, по-

зволяют использовать встроенное ядро Шина АНВ имеет через мост связь • поддержку режимов «ведущий» и

Cortex M0 как для управления блоком с шиной АРВ, к которой подключены «ведомый»;

радиосвязи, так и для исполнения кода цифровые выводы общего назначения

пользовательского приложения. Вну- для входа и выхода (GPIO), часы реаль- • профиль GAP: режим центрально-

тренняя структура BlueNRG-1 пред- ного времени (RTC), сторожевой таймер го, периферийного, наблюдающего или

ставлена рисунке3. К внутренней шине (WDT) и два многофункциональных вещательного узла;

АНВ подключены: ядро СМО, програм- таймера (MFT), а также последователь-

мируемая Flash-память (160 кбайт), ные интерфейсы SPI, UART и I2C для • профиль ATT/GATT: клиент и

24 кбайт быстрой статической памяти соединения с внешней периферией. сервер;

RAM, контроллер DMA, радиомодуль

Микросхемы BlueNRG-1 включают • SM: приватность, аутентификация

стек библиотек программного обеспе- и авторизация;

• L2CAP (управление логическими

связями и протокол адаптации);

НОВОСТИ ЭЛЕКТРОНИКИ № 12, 2016 5